# ΧΑΡΟΚΟΠΕΙΟ ΠΑΝΕΠΙΣΤΗΜΙΟ ΤΜΗΜΑ ΠΛΗΡΟΦΟΡΙΚΗΣ ΚΑΙ ΤΗΛΕΜΑΤΙΚΗΣ

Ενσωμάτωση και εφαρμογή του Μοντέλου Ελέγχου και της Στατικής Ανάλυσης στην Ανάπτυξη Προγραμμάτων για Προγραμματιζόμενους Λογικούς Ελεγκτές

Πτυχιακή εργασία

Τσιπλάκη Σπηλιοπούλου Χριστίνα

Τριμελής Εξεταστική Επιτροπή

Dr. Βαρλάμης Ηρακλής (Επιβλέπων)

Dr. Καμαλάκης Θωμάς

Dr. Μιχαήλ Δημήτριος

#### Περίληψη

Η βιομηχανία εξελίσσεται σε τέτοιο βαθμό όπου η ανθρώπινη παρέμβαση για τη λειτουργεία των συστημάτων, τείνει να εξαφανιστεί με το πέρασμα του χρόνου. Σαν αποτέλεσμα, έστω και το πιο μικρό λάθος σε ένα σύστημα ελέγχου μπορεί να αποβεί μοιραίο. Συνεπώς, η ανάγκη ανάπτυξης ισχυρών, ασφαλών και αξιόπιστων συστημάτων ελέγχου είναι επιτακτική για τους μηχανικούς ελέγχου. Προκειμένου να μπορούν να εγγυηθούν τα παραπάνω, τόσο το λογισμικό (software) όσο και το υλισμικό (hardware) πρέπει να αναλυθούν και να είναι βέβαιο ότι πληρούν τις απαραίτητες προϋποθέσεις.

Η πιο ευρέως διαδεδομένη συσχευή ελέγχου στην βιομηχανία ονομάζεται προγραμματιζόμενος λογικός ελεγχτής (PLC). Τα PLC χρησιμοποιούνται σε όλο το χόσμο σε εχατομμύρια βιομηχανίες και συνεπώς η εγγύηση της ασφάλειας που παρέχει ένα τέτοιο σύστημα αποτελεί μια απαιτητική πρόχληση για τους μηχανιχούς. Δοχιμές και τυπιχές μέθοδοι χρησιμοποιούνται προχειμένου λοιπόν να ελεγχθεί η ορθότητα ενός PLC προγράμματος.

Στόχος αυτής της πτυχιαχής εργασίας είναι η βελτίωση της διασφάλισης των PLC προγραμμάτων και η μείωση των σφαλμάτων που περιέχονται στο λογισμικό τους με την ενσωμάτωση και την εφαρμογή στατικής ανάλυσης κώδικα και μίας τυπικής μεθόδου. Ταυτόχρονα, στόχος της πτυχιαχής είναι μέσα από αυτό να εξαλειφθεί κάθε πολυπλοκότητα από την πλευρά του χρήστη.

Τα πειράματα και οι μεθοδολογίες που χρησιμοποιήθηκαν σε αυτή την πτυχιακή έχουν εφαρμοστεί σε PLC προγράμματα που αναπτύχθηκαν στο CERN και χρησιμοποιούνται στα πειράματα που διεξάγονται καθημερινά.

#### Abstract

Industry processes are evolving to the point where human interventions tend to disappear with the passage of time and as a result even a small mistake in these control systems can have catastrophic consequences. For that reason the need of developing robust, safe and reliable control systems is fundamental for control engineers. To guarantee the above both the hardware and the software have to be analysed to ensure that they fulfil the requirements.

The most popular control device in the process industry is the Programmable Logical Controller (PLC). PLCs are used all over the world for millions of industrial processes. Guaranteeing the safety of such a system is a challenging task for engineers. Testing and formal methods are used to check the correctness of a PLC program and ensure its safety.

The goal of this thesis is to improve the safety assurance of PLC programs and reduce the number of flaws in the software by integrating and applying static analysis and one formal method technique in the development process and at the same time hide any complexity from the developer.

The experiments and the methodologies used in this thesis have been applied to real-life PLC programs developed at CERN.

Η Τσιπλάχη-Σπηλιοπούλου Χριστίνα, δηλώνω υπεύθυνα ότι:

- 1. Είμαι η κάτοχος των πνευματικών δικαιωμάτων της πρωτότυπης αυτής εργασίας και από όσο γνωρίζω η εργασία μου δε συκοφαντεί πρόσωπα, ούτε προσβάλει τα πνευματικά δικαιώματα τρίτων.

- 2. Αποδέχομαι ότι η ΒΚΠ μπορεί, χωρίς να αλλάξει το περιεχόμενο της εργασίας μου, να τη διαθέσει σε ηλεκτρονική μορφή μέσα από τη ψηφιακή Βιβλιοθήκη της, να την αντιγράψει σε οποιοδήποτε μέσο ή/και σε οποιοδήποτε μορφότυπο καθώς και να κρατά περισσότερα από ένα αντίγραφα για λόγους συντήρησης και ασφάλειας.

## Περιεχόμενα

| 1              | Εισαγωγή           |                                                                  |            |  |  |  |  |  |  |

|----------------|--------------------|------------------------------------------------------------------|------------|--|--|--|--|--|--|

|                | 1.1                | Γενικό πλαίσιο                                                   | 8          |  |  |  |  |  |  |

|                | 1.2                | Συνεισφορά και Κίνητρα για την πτυχιακή                          | 9          |  |  |  |  |  |  |

| 2              | Υπο                | Υπόβαθρο                                                         |            |  |  |  |  |  |  |

|                | 2.1                | Εισαγωγή                                                         | 10         |  |  |  |  |  |  |

|                | 2.2                | Programmable Logic Controllers                                   | 10         |  |  |  |  |  |  |

|                |                    | 2.2.1 PLC Hardware                                               | 10         |  |  |  |  |  |  |

|                |                    | 2.2.2 PLC Software                                               | 11         |  |  |  |  |  |  |

|                |                    | 2.2.3 UNICOS                                                     | 12         |  |  |  |  |  |  |

|                | 2.3                | Μοντέλο ελέγχου και Στατική ανάλυση                              | 12         |  |  |  |  |  |  |

|                |                    | · · · · · · · · · · · · · · · · · · ·                            | 12         |  |  |  |  |  |  |

|                |                    | · ·                                                              | 12         |  |  |  |  |  |  |

|                |                    |                                                                  | 13         |  |  |  |  |  |  |

|                | 2.4                |                                                                  | 15         |  |  |  |  |  |  |

|                |                    | 7 1 1 1                                                          | 15         |  |  |  |  |  |  |

|                |                    |                                                                  | 15         |  |  |  |  |  |  |

|                | 2.5                | Παρουσίαση τεχνολογιών που χρησιμοποιήθηκαν για την εκπόνηση της |            |  |  |  |  |  |  |

|                |                    |                                                                  | 16         |  |  |  |  |  |  |

|                |                    | X 12 (1)                                                         | 16         |  |  |  |  |  |  |

|                |                    | 1                                                                | 16         |  |  |  |  |  |  |

|                |                    | 2.5.3 Spoofax                                                    | 16         |  |  |  |  |  |  |

|                |                    | <u>.</u>                                                         | 16         |  |  |  |  |  |  |

|                |                    |                                                                  |            |  |  |  |  |  |  |

| 3              | $\mathbf{E}$ νο    | σωμάτωση του μοντέλου ελέγχου στην ανάπτυξη PLC προ-             |            |  |  |  |  |  |  |

|                | γρα                | μμάτων                                                           | 17         |  |  |  |  |  |  |

|                | 3.1                | Εισαγωγή                                                         | 17         |  |  |  |  |  |  |

|                | 3.2                | Συνεισφορά                                                       | 19         |  |  |  |  |  |  |

|                | 3.3                | • •                                                              | 21         |  |  |  |  |  |  |

| 4              | Υλο                | Υλοποίηση μιας αφηρημένης τεχνικής                               |            |  |  |  |  |  |  |

|                | 4.1                | Εισαγωγή                                                         | 21         |  |  |  |  |  |  |

|                | 4.2                | Συνεισφορά                                                       |            |  |  |  |  |  |  |

| 5              | Στο                | ιτική ανάλυση κώδικα                                             | 27         |  |  |  |  |  |  |

|                | 5.1                | •                                                                | 27         |  |  |  |  |  |  |

|                | 5.2                | • • •                                                            | 27         |  |  |  |  |  |  |

|                | J                  | 270.00.00.00.00.00.00.00.00.00.00.00.00.0                        |            |  |  |  |  |  |  |

| 6              | $\Sigma$ υ $\iota$ | ιπεράσματα και Μελλοντικές επεκτάσεις                            | <b>2</b> 9 |  |  |  |  |  |  |

|                | 6.1                | Συμπεράσματα                                                     | 29         |  |  |  |  |  |  |

|                | 6.2                | Μελλοντικές επεκτάσεις                                           | 30         |  |  |  |  |  |  |

| Α.             |                    | 3:                                                               | 01         |  |  |  |  |  |  |

| $\mathbf{A}$ ] | ppen               | dices                                                            | 31         |  |  |  |  |  |  |

| $\mathbf{A}$   | Intr               |                                                                  | <b>32</b>  |  |  |  |  |  |  |

|                | A.1                | Context                                                          | 33         |  |  |  |  |  |  |

|                | A.2                | Contributions of the Thesis and Motivation                       | 34         |  |  |  |  |  |  |

| В              | Bac                | kground and Related Work                                         | <b>3</b> 6 |  |  |  |  |  |  |

|                | B.1                | Introduction                                                     | 36         |  |  |  |  |  |  |

|                | B.2                | Programmable Logic Controllers                                   | 36         |  |  |  |  |  |  |

|                |                    |                                                                  | 36         |  |  |  |  |  |  |

|                |                    |                                                                  | 37         |  |  |  |  |  |  |

|                |                    |                                                                  | 39         |  |  |  |  |  |  |

|                |                    |                                                                  |            |  |  |  |  |  |  |

| $\mathbf{C}$ | Mod    | del Checking and Static Analysis                                    | 39        |

|--------------|--------|---------------------------------------------------------------------|-----------|

|              | C.1    | Formal Methods                                                      | 39        |

|              |        | C.1.1 Model checking                                                | 39        |

|              |        | C.1.2 Static analysis                                               | 41        |

|              |        |                                                                     |           |

| $\mathbf{D}$ | Rela   | ated Work                                                           | 42        |

|              | D.1    | Model checking applied to PLC programs                              | 43        |

|              | D.2    |                                                                     |           |

|              | D.2    | because analysis applied to 120 programs                            | 10        |

| $\mathbf{E}$ | Tecl   | hnologies used for this thesis                                      | 43        |

| _            | E.1    | Apache Subversion                                                   | 43        |

|              | E.2    | Jenkins                                                             | 44        |

|              |        |                                                                     |           |

|              | E.3    | Spoofax                                                             | 44        |

|              | E.4    | Xtext                                                               | 44        |

| T-3          | T 4    |                                                                     |           |

| $\mathbf{F}$ |        | egration of Model Checking in the development of PLC pro-           |           |

|              | grar   |                                                                     | 45        |

|              | F.1    | Introduction                                                        | 45        |

|              | F.2    | Contribution                                                        | 49        |

|              | F.3    | Conclusions                                                         | 52        |

|              |        |                                                                     |           |

| $\mathbf{G}$ | Imp    | lementation of an Abstraction Technique                             | <b>53</b> |

|              | _      | Introduction                                                        | 53        |

|              |        | Contribution                                                        | 54        |

|              |        |                                                                     |           |

|              | G.3    | I                                                                   | 60        |

|              | G.4    | Analysis and Conclusions                                            | 64        |

| тт           | CI . I | 's Calla Assal at                                                   | <b></b>   |

| Н            |        | cic Code Analysis                                                   | 65        |

|              | H.1    | Introduction                                                        | 65        |

|              | H.2    | Static analysis tools evaluation                                    | 65        |

|              | H.3    | Contribution                                                        | 66        |

|              |        | H.3.1 Introduction                                                  | 66        |

|              |        | H.3.2 Spoofax approach                                              | 69        |

|              |        | H.3.3 PLCverif approach                                             | 76        |

|              | ци     | Analysis and conclusions                                            |           |

|              | п.4    | Analysis and conclusions                                            | 00        |

| Ι            | Con    | clusions and future work                                            | 82        |

| •            | I.1    | Conclusions                                                         | 82        |

|              |        |                                                                     |           |

|              | I.2    | Future work                                                         | 82        |

|              |        |                                                                     |           |

| <b>T</b> /   |        | (A) \(\nabla_1 \)                                                   |           |

| Ŋ            | ατ     | άλογος Σχημάτων                                                     |           |

|              |        |                                                                     | _         |

|              | 1      | Πυραμίδα επιπέδων των στυστημάτων ελέγχου                           |           |

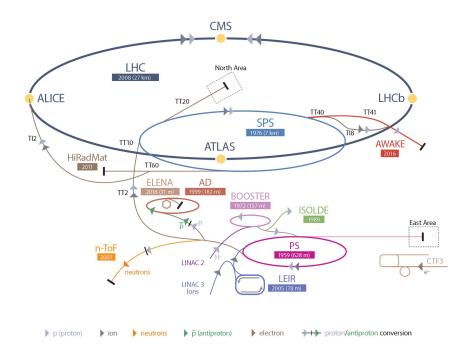

|              | 2      | CERN accelerator complex [14]                                       | 9         |

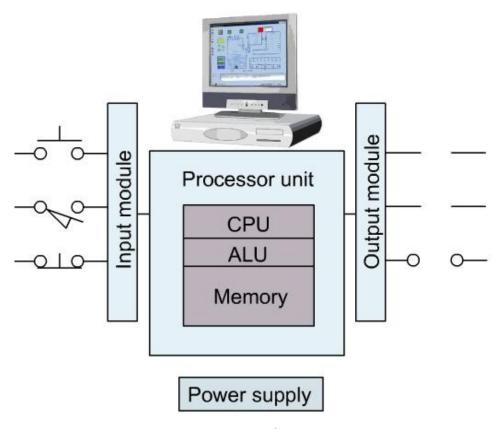

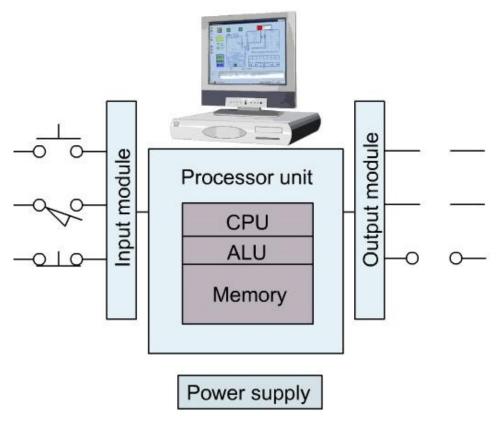

|              | 3      | Basic PLC components                                                | 11        |

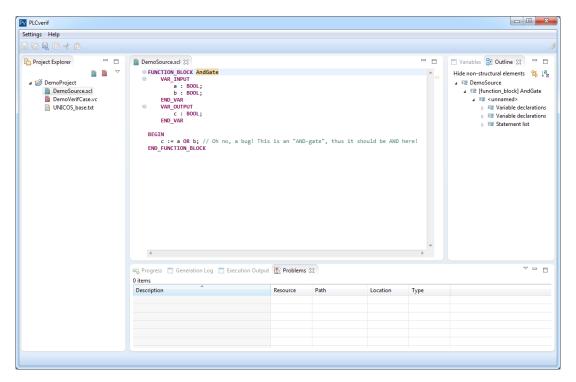

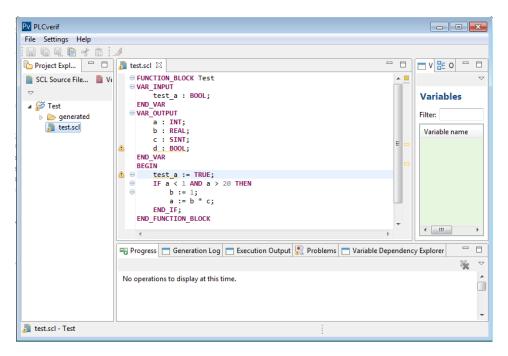

|              | 4      | SCL editor                                                          | 18        |

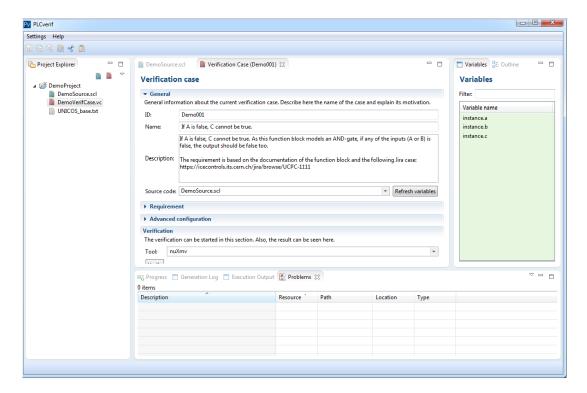

|              | 5      | Περίπτωση επαλήθευσης                                               | 18        |

|              | 6      | · · · · · · · · · · · · · · · · · · ·                               | 19        |

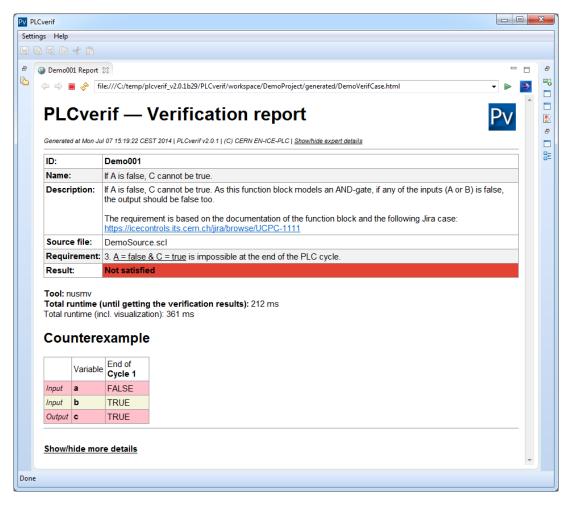

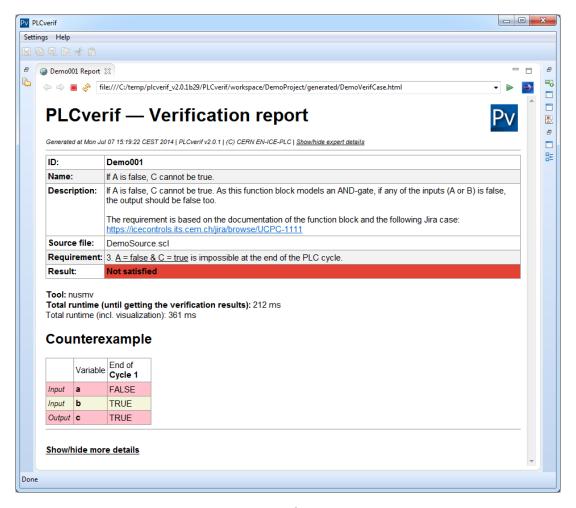

|              |        | Αναφορά επαλήθευσης                                                 |           |

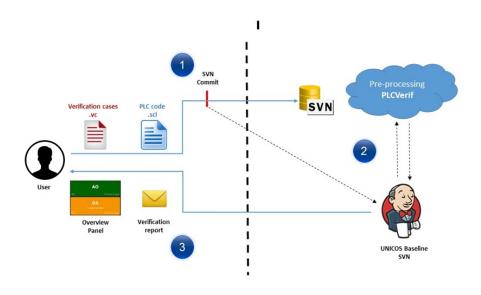

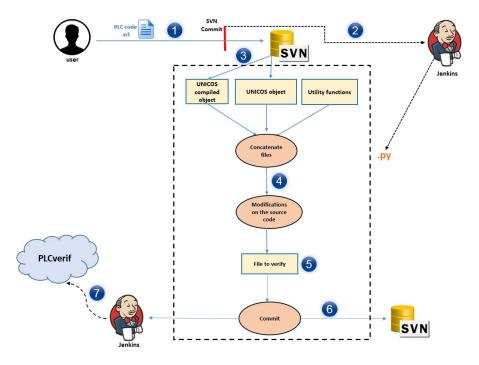

|              | 7      | Επισχόπηση της προσέγγισης                                          | 20        |

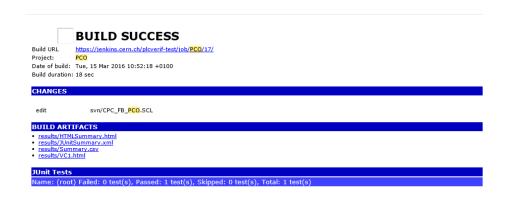

|              | 8      | Παράδειγμα αναφοράς της ανάλυσης της περίπτωσης επαλήθευσης που     |           |

|              |        | αποστέλλεται στο χρήστη με email                                    | 20        |

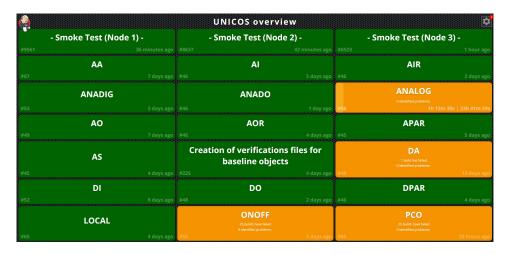

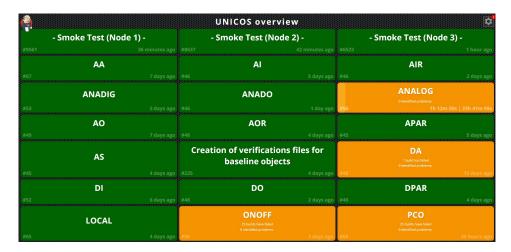

|              | 9      | UNICOS πάνελ επισκόπησης των πρότζεκτ                               | 21        |

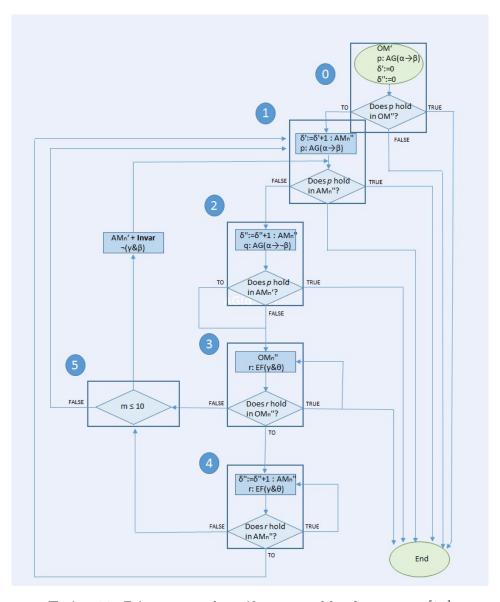

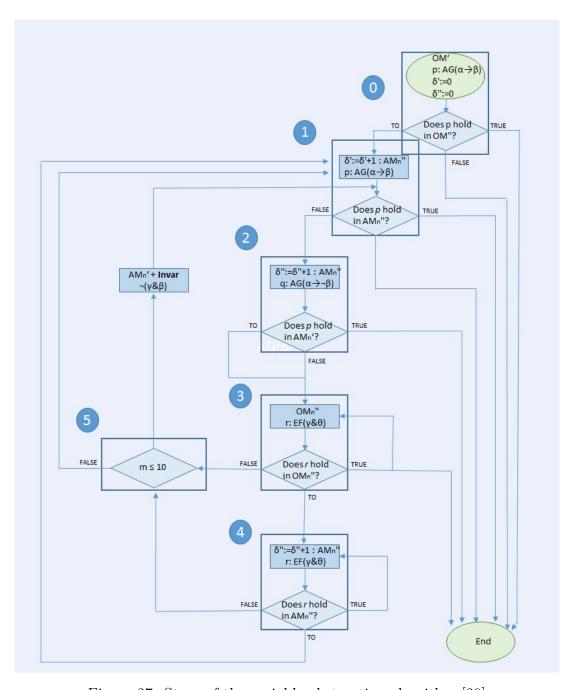

|              | 10     | Βήματα του αλγορίθμου variable abstraction [20]                     | 22        |

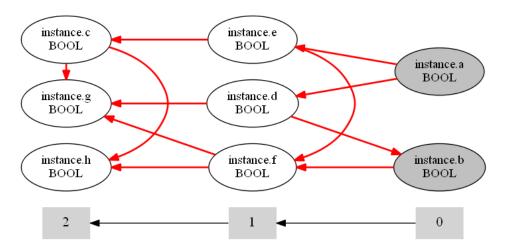

|              | 11     | Το παραγόμενο Variable dependency graph από το παράδειγμα του List- | _         |

|              |        | ing 5                                                               | 24        |

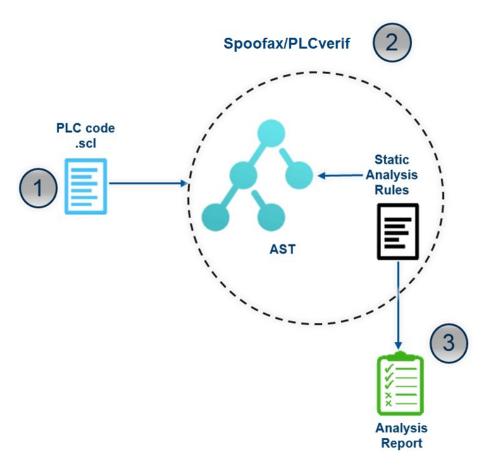

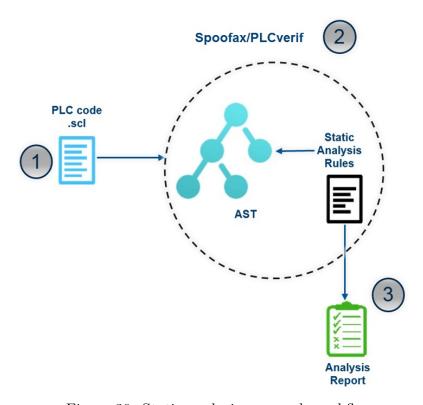

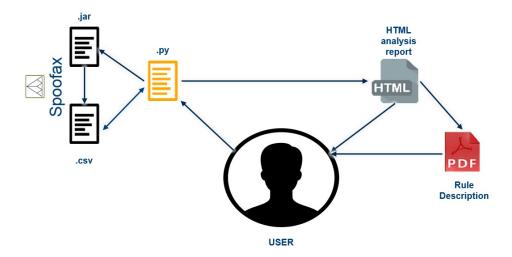

|              | 12     | Ροή εργασιών για τις προσεγγίσεις του εργαλείου στατικής ανάλυσης.  | 28        |

|              | 14     | τοη εργασίων για τις προσεγγισεις του εργαπείου οτατικής αναπυσής   | 40        |

| 13                                                                                              | Control system layers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 32                                                                               |

|-------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------|

| 14                                                                                              | CERN accelerator complex [14]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 34                                                                               |

| 15                                                                                              | Basic PLC components                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 37                                                                               |

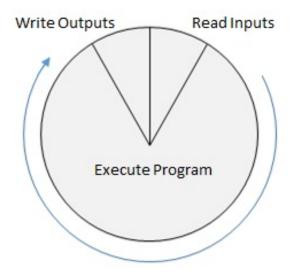

| 16                                                                                              | Schema of the cyclic scanning mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 38                                                                               |

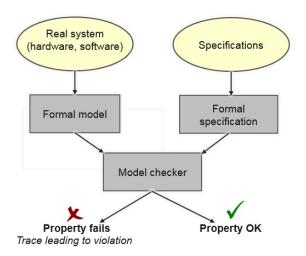

| 17                                                                                              | Model checker process                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 40                                                                               |

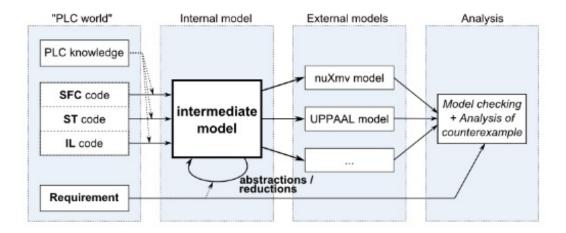

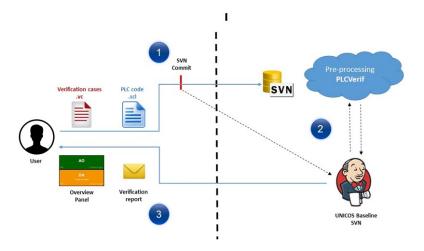

| 18                                                                                              | Methodology overview                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 46                                                                               |

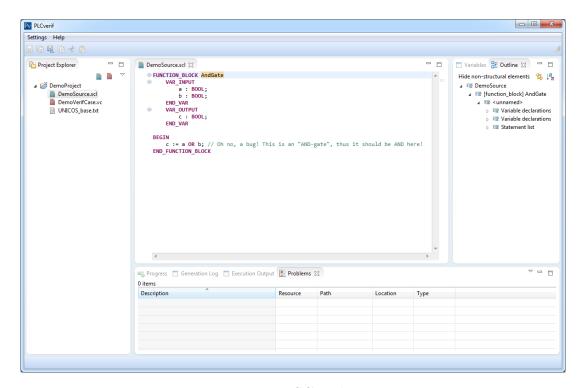

| 19                                                                                              | SCL editor                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 46                                                                               |

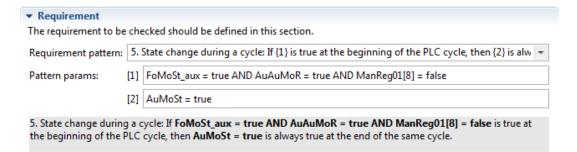

| 20                                                                                              | Requirement pattern                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 47                                                                               |

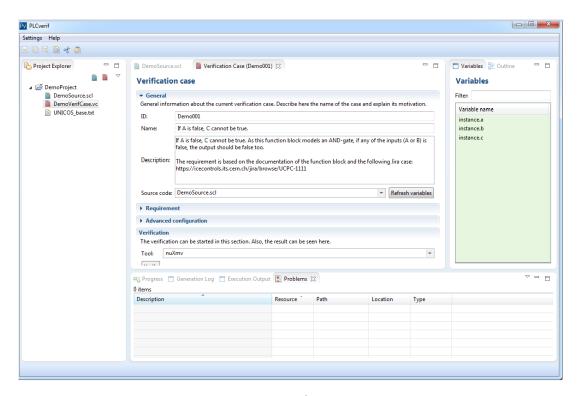

| 21                                                                                              | Verification case                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 47                                                                               |

| 22                                                                                              | Verification report                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 48                                                                               |

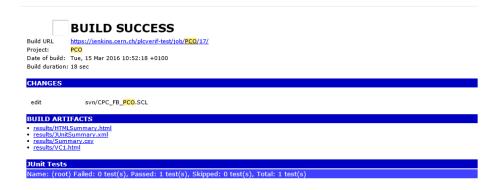

| 23                                                                                              | Example of an email report provided by Jenkins to the user after                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                  |

|                                                                                                 | modification on the PLC source code                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                  |

| 24                                                                                              | UNICOS overview panel                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                  |

| 25                                                                                              | High level overview of the approach                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                  |

| 26                                                                                              | User workflow                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                  |

| 27                                                                                              | Steps of the variable abstraction algorithm [20]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                  |

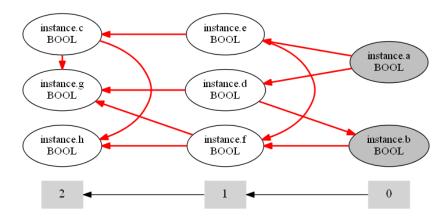

| 28                                                                                              | Variable dependency graph example of Listing 5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 58                                                                               |

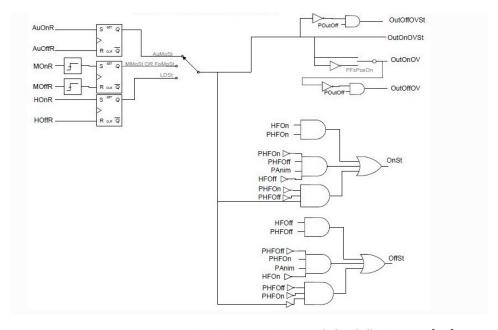

| 29                                                                                              | Position calculation schema of OnOff object. [40]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 61                                                                               |

| 30                                                                                              | Static analysis approach workflow                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                  |

| 31                                                                                              | User workflow for the Java approach                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                  |

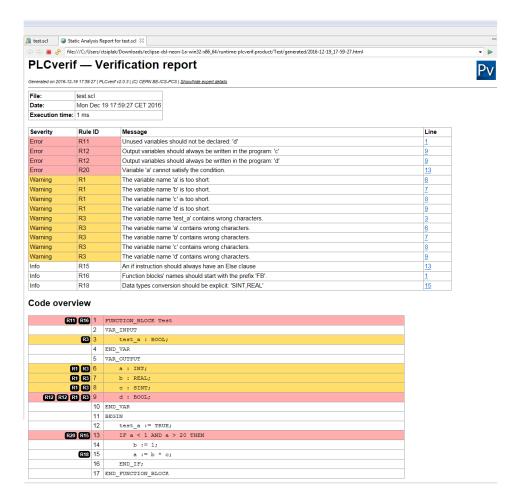

| 32                                                                                              | Static analysis report.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                  |

| 33                                                                                              | SLC editor in PLCverif approach of static analysis tool                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                  |

| 34                                                                                              | Static analysis report produced by PLCverif                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 80                                                                               |

| $K_{\sim \tau}$                                                                                 | άλογος Πινάκων                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                  |

|                                                                                                 | ·                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                  |

| 1                                                                                               | Πίνακας σύγκρισης Ι των εργαλείων στατικής ανάλυσης για προγράμματα                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 27                                                                               |

|                                                                                                 | Πίνακας σύγκρισης Ι των εργαλείων στατικής ανάλυσης για προγράμματα PLC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 27                                                                               |

| 1                                                                                               | Πίνακας σύγκρισης Ι των εργαλείων στατικής ανάλυσης για προγράμματα PLC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                  |

| 1                                                                                               | Πίνακας σύγκρισης Ι των εργαλείων στατικής ανάλυσης για προγράμματα PLC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                  |

| 1<br>2                                                                                          | Πίνακας σύγκρισης Ι των εργαλείων στατικής ανάλυσης για προγράμματα PLC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 27                                                                               |

| 1<br>2                                                                                          | Πίνακας σύγκρισης $I$ των εργαλείων στατικής ανάλυσης για προγράμματα $PLC$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 27<br>29                                                                         |

| 1<br>2<br>3                                                                                     | Πίνακας σύγκρισης $I$ των εργαλείων στατικής ανάλυσης για προγράμματα $PLC$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 27<br>29<br>59                                                                   |

| 1<br>2<br>3<br>4                                                                                | Πίνακας σύγκρισης Ι των εργαλείων στατικής ανάλυσης για προγράμματα $PLC$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 27<br>29<br>59<br>59                                                             |

| 1<br>2<br>3<br>4<br>5                                                                           | Πίνακας σύγκρισης Ι των εργαλείων στατικής ανάλυσης για προγράμματα PLC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 27<br>29<br>59<br>59<br>60                                                       |

| 1<br>2<br>3<br>4<br>5<br>6                                                                      | Πίναχας σύγκρισης Ι των εργαλείων στατικής ανάλυσης για προγράμματα PLC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 27<br>29<br>59<br>59<br>60                                                       |

| 1<br>2<br>3<br>4<br>5<br>6<br>7                                                                 | Πίναχας σύγκρισης Ι των εργαλείων στατικής ανάλυσης για προγράμματα PLC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 27<br>29<br>59<br>59<br>60<br>62                                                 |

| 1<br>2<br>3<br>4<br>5<br>6<br>7<br>8<br>9<br>10                                                 | Πίναχας σύγκρισης $I$ των εργαλείων στατικής ανάλυσης για προγράμματα $PLC$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 27 29 59 60 62 62 63 63                                                          |

| 1<br>2<br>3<br>4<br>5<br>6<br>7<br>8<br>9<br>10<br>11                                           | Πίναχας σύγχρισης $I$ των εργαλείων στατιχής ανάλυσης για προγράμματα $PLC$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 27 29 59 60 62 63 63 63                                                          |

| 1<br>2<br>3<br>4<br>5<br>6<br>7<br>8<br>9<br>10<br>11<br>12                                     | Πίναχας σύγκρισης $I$ των εργαλείων στατικής ανάλυσης για προγράμματα $PLC$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 27<br>29<br>59<br>60<br>62<br>63<br>63<br>63<br>64                               |

| 1<br>2<br>3<br>4<br>5<br>6<br>7<br>8<br>9<br>10<br>11<br>12<br>13                               | Πίναχας σύγκρισης $I$ των εργαλείων στατικής ανάλυσης για προγράμματα $PLC$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 27<br>29<br>59<br>60<br>62<br>63<br>63<br>63<br>64<br>66                         |

| 1<br>2<br>3<br>4<br>5<br>6<br>7<br>8<br>9<br>10<br>11<br>12<br>13<br>14                         | Πίναχας σύγκρισης Ι των εργαλείων στατικής ανάλυσης για προγράμματα PLC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 27<br>29<br>59<br>60<br>62<br>63<br>63<br>64<br>66<br>66                         |

| 1<br>2<br>3<br>4<br>5<br>6<br>7<br>8<br>9<br>10<br>11<br>12<br>13<br>14<br>15                   | Πίναχας σύγκρισης $I$ των εργαλείων στατικής ανάλυσης για προγράμματα $PLC$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 27<br>29<br>59<br>60<br>62<br>63<br>63<br>64<br>66<br>66<br>81                   |

| 1<br>2<br>3<br>4<br>5<br>6<br>7<br>8<br>9<br>10<br>11<br>12<br>13<br>14<br>15<br>16             | Πίναχας σύγκρισης $I$ των εργαλείων στατικής ανάλυσης για προγράμματα $PLC$ .  Πίναχας σύγκρισης $II$ των εργαλείων στατικής ανάλυσης για προγράμματα $PLC$ .  Σύγκριση μεταξύ των προσεγγίσεων για το εργαλείο στατικής ανάλυσης κώδικα.  Counterexample for $p$ on $AM_1'$ 1 invariant.  Counterexample for $p$ on $AM_1'$ + 1 invariants.  PCO UNICOS object tested with nuXmv $IC3$ algorithm.  PCO UNICOS object tested with nuXmv $IC3$ algorithm.  ANALOG UNICOS object tested with nuXmv $IC3$ algorithm.  ANALOG UNICOS object tested with nuXmv $IC3$ algorithm.  ONOFF UNICOS object tested with nuXmv $IC3$ algorithm.  ONOFF UNICOS object tested with nuXmv $IC3$ algorithm.  ONOFF UNICOS object tested with nuXmv $IC3$ algorithm.  Comparison table $I$ of existed static analysis tools for $IC3$ programs.  Comparison table $I$ of existed static analysis tools for $IC3$ programs.  Comparison between static analysis approaches.  PCO requirements tested with nuXmv $IC3$ . | 27<br>29<br>59<br>60<br>62<br>63<br>63<br>64<br>66<br>66<br>81<br>97             |

| 1<br>2<br>3<br>4<br>5<br>6<br>7<br>8<br>9<br>10<br>11<br>12<br>13<br>14<br>15<br>16<br>17       | Πίναχας σύγχρισης $I$ των εργαλείων στατιχής ανάλυσης για προγράμματα $PLC$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 27<br>29<br>59<br>60<br>62<br>63<br>63<br>64<br>66<br>66<br>81<br>97             |

| 1<br>2<br>3<br>4<br>5<br>6<br>7<br>8<br>9<br>10<br>11<br>12<br>13<br>14<br>15<br>16<br>17<br>18 | Πίνακας σύγκρισης Ι των εργαλείων στατικής ανάλυσης για προγράμματα $PLC$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 27<br>29<br>59<br>60<br>62<br>63<br>63<br>64<br>66<br>66<br>81<br>97<br>98<br>99 |

| 1<br>2<br>3<br>4<br>5<br>6<br>7<br>8<br>9<br>10<br>11<br>12<br>13<br>14<br>15<br>16<br>17       | Πίναχας σύγχρισης $I$ των εργαλείων στατιχής ανάλυσης για προγράμματα $PLC$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 27<br>29<br>59<br>60<br>62<br>63<br>63<br>64<br>66<br>66<br>81<br>97<br>98<br>99 |

## 1 Εισαγωγή

Η τεχνολογία, εξελισσόμενη με ταχείς ρυθμούς τις τελευταίες δεκαετίες, έχει επηρεάσει σχεδόν κάθε πτυχή της καθημερινής μας ζωής. Μετά τον 18ο αιώνα η βιομηχανική επανάσταση σφράγισε σε μεγάλο βαθμό την ιστορία καθώς αποτέλεσε το έδαφος για οικονομικές, πολιτικές και κοινωνικές αλλαγές. Ακόμα, η αυτοματοποίηση έφερε και συνεχίζει να φέρνει οφέλη στην ανθρώπινη κοινωνία.

Η βιομηχανική αυτοματοποίηση εξελίσσεται και αποτελεί ένα σημαντικό παράγοντα στην ανάπτυξη του βιομηχανικού τομέα. Παίζει σημαντικό ρόλο στην βελτίωση της καθημερινής μας ζωής πράγμα που αποδεικνύεται και από το γεγονός ότι ο μέσος όρος ζωής και ο δείκτης πληθυσμού άρχισαν να αυξάνονται χάρη στην ανάπτυξη νέων τεχνολογιών και συσκευών. Πιο συγκεκριμένα, το μεσο βιοτικό επίπεδο και ο δείκτης πληθυσμού άρχισαν να αυξάνονται χάρη στην ανάπτυξη νέων τεχνολογιών και συσκευών. Εισάγοντας στην βιομηχανία την αυτοματοποίηση, η παρέμβαση του ανθρώπου μειώθηκε ή και αντικαταστάθηκε από αυτοματοποιημένες λειτουργίες όταν επρόκειτο για επικίνδυνες εργασίες.

Η βιομηχανική αυτοματοποίηση, ήρθε να 'ελευθερώσει' τους ανθρώπους από την κουραστική και πολύωρη επιτήρηση εργασιών που σχετίζονται με την αλληλεπίδραση μεταξύ αυτών και των συστημάτων ελέγχου. Η υπάρχουσα θεωρία αλλά και οι τεχνολογίες γύρω από τα συστήματα ελέγχου αποτελούν τη βάση για το σχεδιασμό συστημάτων με τις επιθυμητές συμπεριφορές τα οποία δεν χρειάζονται την επέμβαση του ανθρώπινου παράγοντα για να λειτουργήσουν.

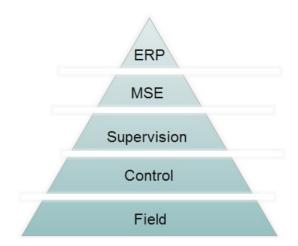

Γενικότερα, τα συστήματα ελέγχου χωρίζονται σε τρεις βασικές κατηγορίες:

- 1. Συστήματα εποπτείας (supervision): σε αυτό το επίπεδο, το εργαλείο εποπτείας που συνήθως ονομάζεται SCADA παρέχει τη διεπαφή με τον χειριστή των διεργασιών.

- 2. Συστήματα ελέγχου (control): αυτό το επίπεδο αποτελείται από τις συσκευές ελέγχου (π.χ. PLC) οι οποίες περίεχουν την λογική για να αυτοματοποιηθεί μία διεργασία.

- 3. Πεδίο ελέγχου (field): αυτό το επίπεδο συντάσεται από αισθητήρες και ενεργοποιητές οι οποίοι λαμβάνουν τις πληροφορίες απο την διεργασία και εκτελούν την λογική που παρέχεται από τις συσκευές ελέγχου.

Παρ΄ όλα αυτά, τα σύγχρονα συστήματα ελέγχου χωρίζονται σε πέντε μέρη αντί για τρία συμπεριλαμβάνοντας επισης το επίπεδο επιχείρησης (Enterprise Resource Planning) και το επίπεδο εργοστασίου (Manufacturing Execution System). Τα επίπεδα ενός σύγχρονου συστήματος ελέγχου παρουσιάζονται στο Σχήμα 1.

Σχήμα 1: Πυραμίδα επιπέδων των στυστημάτων ελέγχου

Από το 1968, οταν ο πρωτος προγραμματιζόμενος λογικός ελεγκτής χρησιμοποιήθηκε για να ελέγχει συστήματα σε βιομηχανίες, περισσότερα κριτικά συστήματα άρχισαν να αυτοματοποιούνται. Καθώς ένα πιθανό σφάλμα σε οποιοδήποτε απο αυτά τα συστήματα μπορεί να προκαλέσει ανεπανόρθωτες ζημιές τόσο στο ανθρώπινο είδος όσο

και στο περιβάλλον και την οικονομία, η ανάγκη για τη διασφάλιση της ποιότητας τους είναι επιτακτική.

Ένα από τα πολλά παραδείγματα είναι ένα λάθος στο λογισμικό που προκάλεσε το ατύχημα του Mars Climate Orbiter [58], ένα ρομποτικό διαστημόπλοιο που εκτοξεύθηκε από τη NASA το Δεκέμβριο του 1998 για να ερευνήσει το Αρειανό κλίμα. Μία μαθηματική ασυμφωνία κόστισε στη NASA ενα διαστημόπλοιο \$125-εκατομμυρίων. Ένα ακόμη παράδειγμα που κόστισε τη ζωή 6 ανθρώπων είναι το σφάλμα που εντοπίστηκε στο λογισμικό της ραδιενεργού μηχανής Therac-25 [61] η οποία χρησιμοποιούνταν για θεραπεία ασθενών με καρκίνο. Εξαιτίας ενός λάθος υπολογισμού η μηχανή χορηγούσε τεράστιες ποσότητες ραδιενέργειας στους ασθενείς.

Στόχος αυτής της πτυχιακής εργασίας είναι η ανάλυση PLC προγραμμάτων και η βελτίωση της ποιότητας τους, εστιάζοντας στη μείωση των σφαλμάτων στο λογισμικό. Τα PLC είναι οι πιο διαδεδομένες συσκευές ελέγχου που χρησιμοποιούνται στη βιομηχανία και τα τελευταία χρόνια γίνονται όλο και πιο διαδεδομένοι στα Safety Instrumented Systems, συστήματα που σχεδιάστηκαν προκειμένου να εγγυώνται την ασφάλεια και την αξιοπιστία των διεργασιών και καθορίζονται απο τις προδιαγραφές των προτύπωνΙΕC 61511 και IEC 61508.

#### 1.1 Γενικό πλαίσιο

Καθώς τα συστήματα ελέγχου χρησιμοποιούνται σε μεγάλο βαθμό όχι μόνο στη βιομηχανία αλλά και σε τομείς όπως η αεροναυπηγική και οι πυρηνικές εγκαταστάσεις, είναι σημαντικό να αποτραπούν λάθη σαν τα προαναφερθέντα. Παρ΄όλα αυτά μόνο λίγες εταιρίες και ερευνητικά κέντρα εμπλέκονται στο συγκεκριμένο πρόβλημα και το CERN (European Organization for Nuclear Research) είναι ένα απο αυτά.

Το παρόν πόνημα, αποτελεί την πτυχιαχή μου εργασία την οποία εκπόνησα στο τελευταίο έτος των σπουδών μου στο Χαροκόπειο Πανεπιστήμιο στο τμήμα Πληροφορικής και Τηλεματικής και η οποία εφαρμόστηκε στα PLC προγράμματα που χρησιμοποιούνται στο CERN . Το CERN το οποίο ιδρύθηκε το 1954, αποτελεί το μεγαλύτερο εργαστήριο σωματιδιαχής φυσικής στην Ευρώπη και βρίσκεται στα Γαλλο-Ελβετικά σύνορα. Η κύρια λειτουργία του αφορά την παροχή επιταχυντών σωματιδίων και άλλων υλικοτεχνικών υποδομών που χρειάζονται για την πειραματική έρευνα στο πεδίο της φυσικής υψηλών ενεργειών.

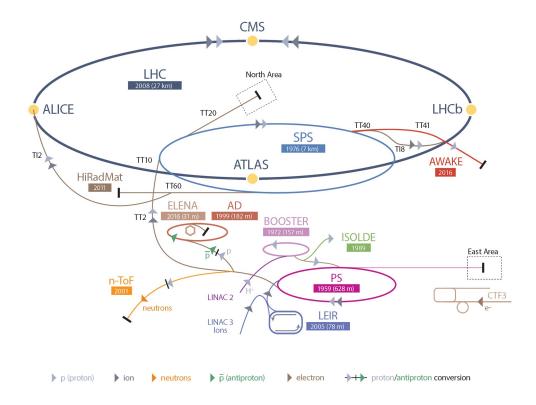

Είναι πανάρχαια η ανάγκη των ανθρώπων να δώσουν απάντηση στο ερώτημα "Πώς δημιουργήθηκε το σύμπαν και η ζωή' και είναι διαρκής η προσπάθεια τους να ανακαλύψουν όσο γίνεται περισσότερα στοιχεία που θα τους επιτρέψουν να απαντήσουν. Ο LHC (Large Hadron Collider) (Σχήμα 2), αυτή τη στιγμή αποτελεί τον μεγαλύτερο επιταχυντή αδρονίων στον κόσμο, βρίσκεται 100 μέτρα υπό το έδαφος και έχει διάμετρο 27 χιλιομέτρων. Ο βασικός του στόχος είναι να αναπαράξει τις συνθήκες που δημιουργήθηκαν αμέσως μετά την μεγάλη έκρηξη (Big Bang). Ο επιταχυντής χρησιμοποιείται κυρίως για την έρευνα φαινομένων που θα προχύψουν από τη σύγκρουση δεσμών πρωτονίων-πρωτονίων, σε πολύ μεγάλες ενέργειες ελαφρώς μικρότερες από την ταχύτητα του φωτός. Εφτά πειράματα (CMS, ATLAS, LHCb, MoEDAL, TOTEM, LHC-forward and ALICE) είναι τοποθετημένα γύρω από τον επιταχυντή και το καθένα από αυτά μελετά τις συγκρούσεις από διαφορετική διάσταση και με διαφορετικές τεχνολογίες. Αναλύοντας τις συγκρούσεις οι επιστήμονες στοχεύουν στο να αποδείξουν ή να διαψεύσουν ποικίλες θεωρίες γύρω από το τομέα τις φυσικής αλλά και να κατανοήσουν τον κόσμο καλύτερα.

Προχειμένου να παρέχουν τις βέλτιστες συνθήχες για τους επιταχυντές, χρησιμοποιούνται βιομηχανικές διεργασίες (εξαερισμός, ψύξη, κρυογονική). Μεταξύ άλλων η πιο διαδεδομένη συσκευή ελέγχου που χρησιμοποιείται στο CERN για τις βιομηχανικές διεργασίες και τις ανάγκες των πειραμάτων είναι το PLC. Το PLC είναι μία ισχυρή συσκευή ελέγχου που διαβάζει καταχωρήσεις (inputs) απο συσκευές τροφοδοσίας (π.χ. διαλογείς, βαλβίδες, αισθητήρες), τις επεξεργάζεταικαι μεταδίδει τα αποτελέσματα σε άλλα συστήματα.

Περισσότερα από 1000 PLC διατηρούνται και χρησιμοποιούνται στο CERN και περίπου το 1/3 αυτών συντηρείται από το γκρουπ Industrial Control and Safety (ICS) που βρίσκεται στο beams (BE) τμήμα. Πιο συγκεκριμένα, το τμήμα Process Control Systems section (PCS) αναπτύσσει, εφαρμόζει και συντηρεί τις εφαρμογές ελέγχου. Το θέμα της πτυχιακής εργασίας σχετίζεται με τις εργασίες του παραπάνω τμήματος και στοχεύει να βελτιώσει την ποιότητα του λογισμικου των PLC εισάγοντας τις τυπικές μεθόδους – και πιο συγκεκριμένα τον έλεγχο μοντέλων (model checking) – και την στατική ανάλυση κώδικα στην προγραμματιστική διαδικασία.

Figure 2: CERN accelerator complex [14]

## 1.2 Συνεισφορά και Κίνητρα για την πτυχιακή